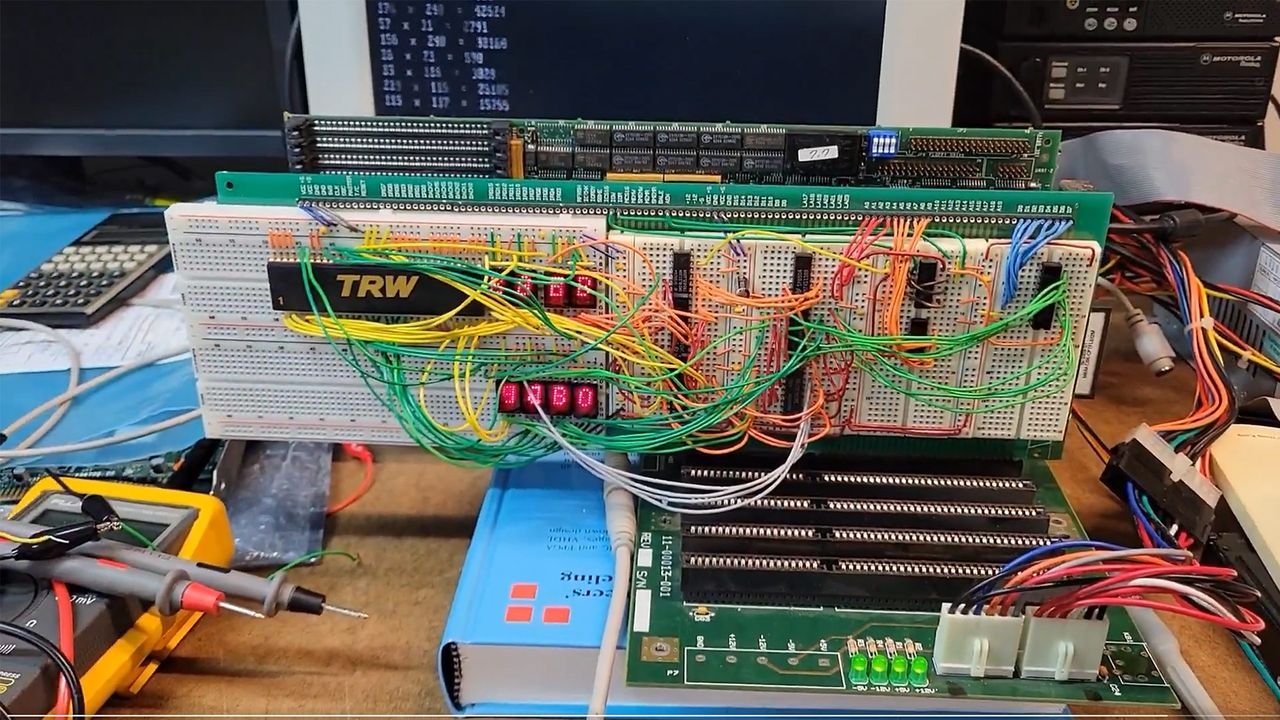

O chip multiplicador paralelo TRW MPY12HJ 12×12, da era original, intercepta instruções MUL da CPU, mas exige modificações no código.

Hardware de 50 anos pode ser lento, mas entusiastas como @bradthx (Brad) estão inovando! Ele demonstrou um acelerador de multiplicação para sistemas Intel 8086 e 8088.

O chip TRW MPY12HJ, presente no mercado entre o final dos anos 70 e início dos 80, poderia ter sido usado em computadores como o IBM PC Model 5150, que popularizou os slots ISA em 1981.

A motivação de Brad era a ineficiência da instrução MUL nos primeiros chips x86. Nesses sistemas, a multiplicação era um processo lento de “shift/add” controlado por microcódigo, similar a resolver a operação manualmente em binário.

A velocidade do TRW permite calcular instruções MUL entre ciclos de barramento, minimizando a penalidade de performance da placa ISA. O resultado é um ganho de 2.5x em comparação com o multiplicador interno da CPU.

Embora não seja essencial hoje, Brad afirma que o projeto valeu a pena. A demonstração revela que a exibição dos cálculos na tela é o principal gargalo de performance.

A placa aceleradora não funciona com aplicativos clássicos já compilados. Ela requer acesso ao código-fonte ou sub-rotinas personalizadas.

Brad esclarece que programas novos ou modificados podem utilizar o hardware multiplicador. No entanto, aplicativos pré-compilados não reconhecem nem utilizam a placa aceleradora ISA.